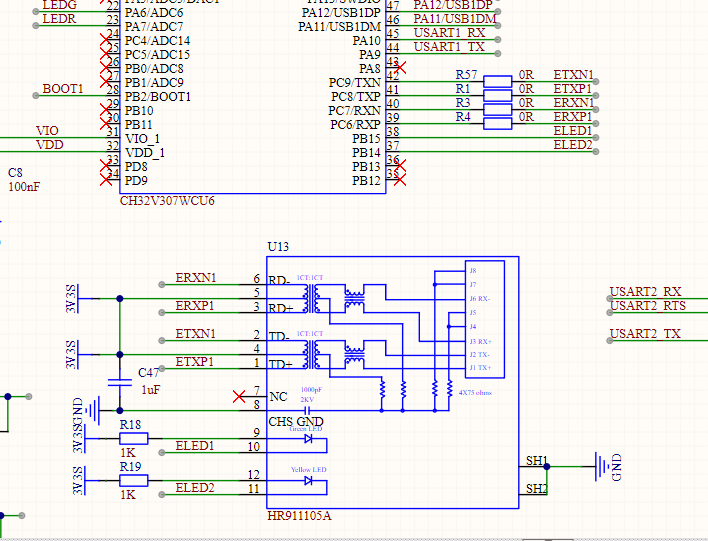

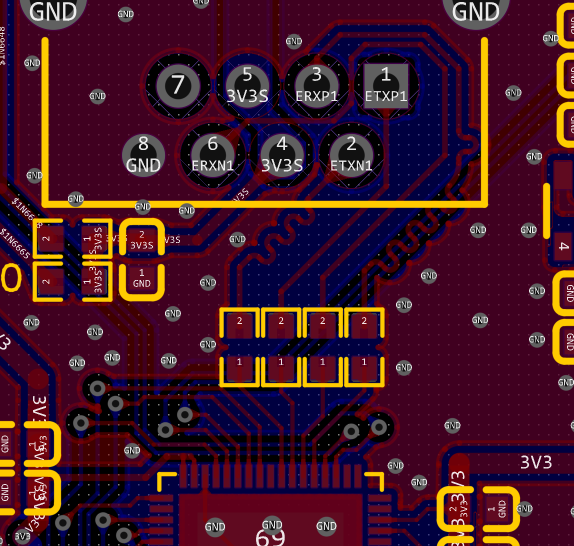

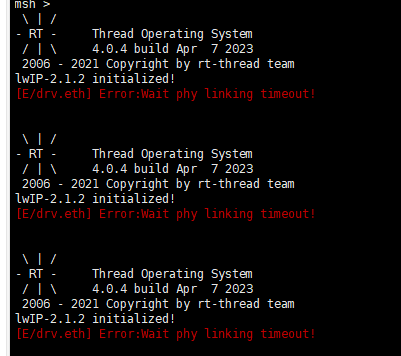

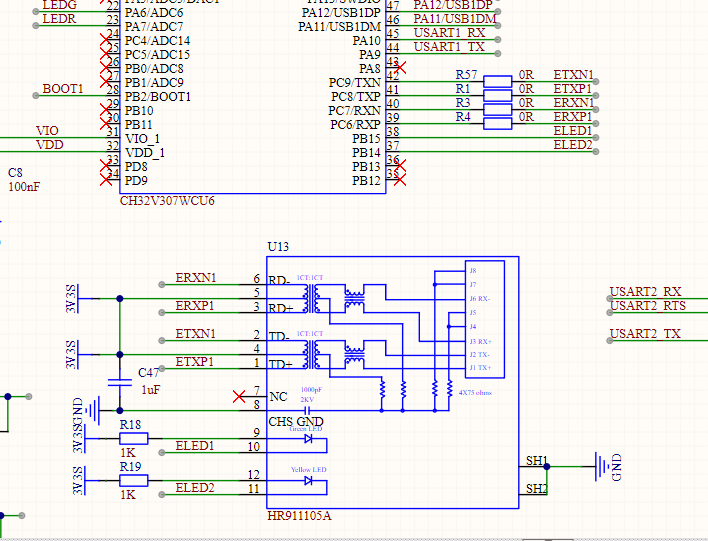

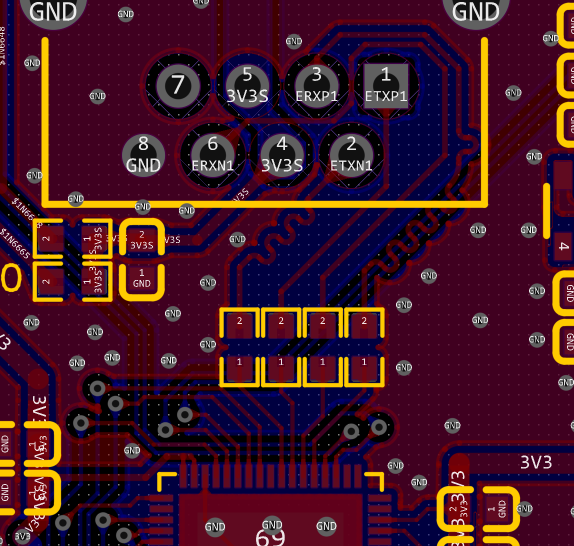

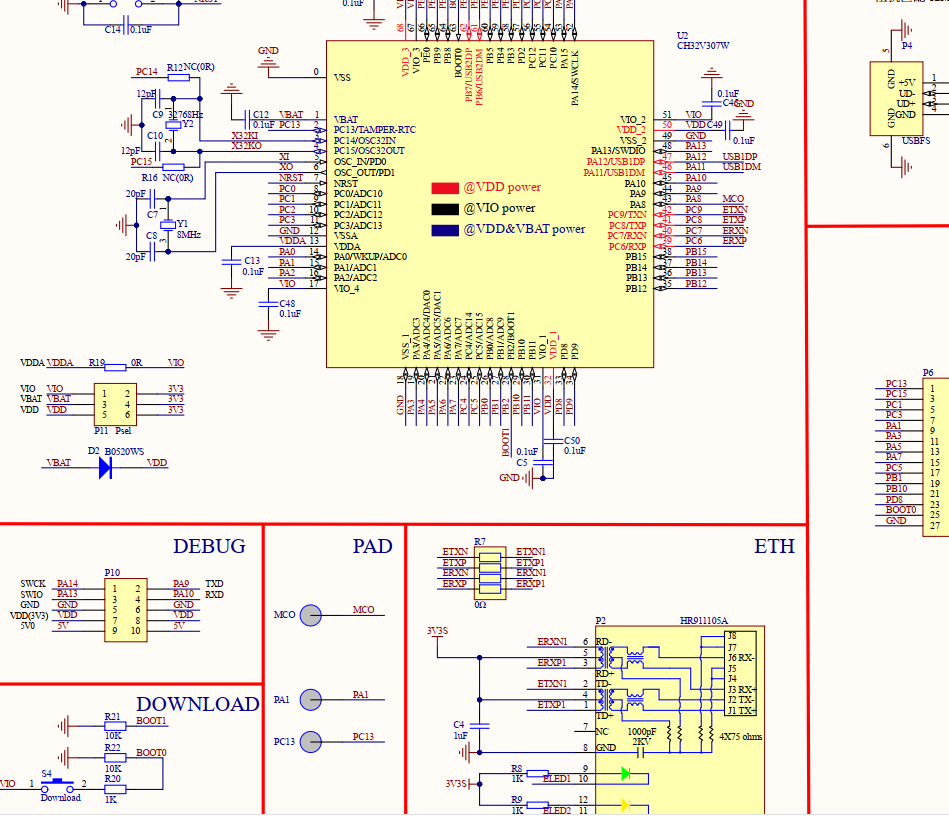

公司项目的需要自己划了一块ch32v307wcu7的板子,使用内置10MPHY,软件跑的是rt-thread的历程,用ch32v307vct6的官方开发板一点问题没有,我对照我原理图和开发板原理图是一样的,但是我画的板子就是不能成功,请问应该怎么解决这个问题,还是需要那里要设置,但是官方开发板都能正常使用,晶振使用的是12M,困惑很久了,不知道问题出在哪里,希望能达到回复

公司项目的需要自己划了一块ch32v307wcu7的板子,使用内置10MPHY,软件跑的是rt-thread的历程,用ch32v307vct6的官方开发板一点问题没有,我对照我原理图和开发板原理图是一样的,但是我画的板子就是不能成功,请问应该怎么解决这个问题,还是需要那里要设置,但是官方开发板都能正常使用,晶振使用的是12M,困惑很久了,不知道问题出在哪里,希望能达到回复

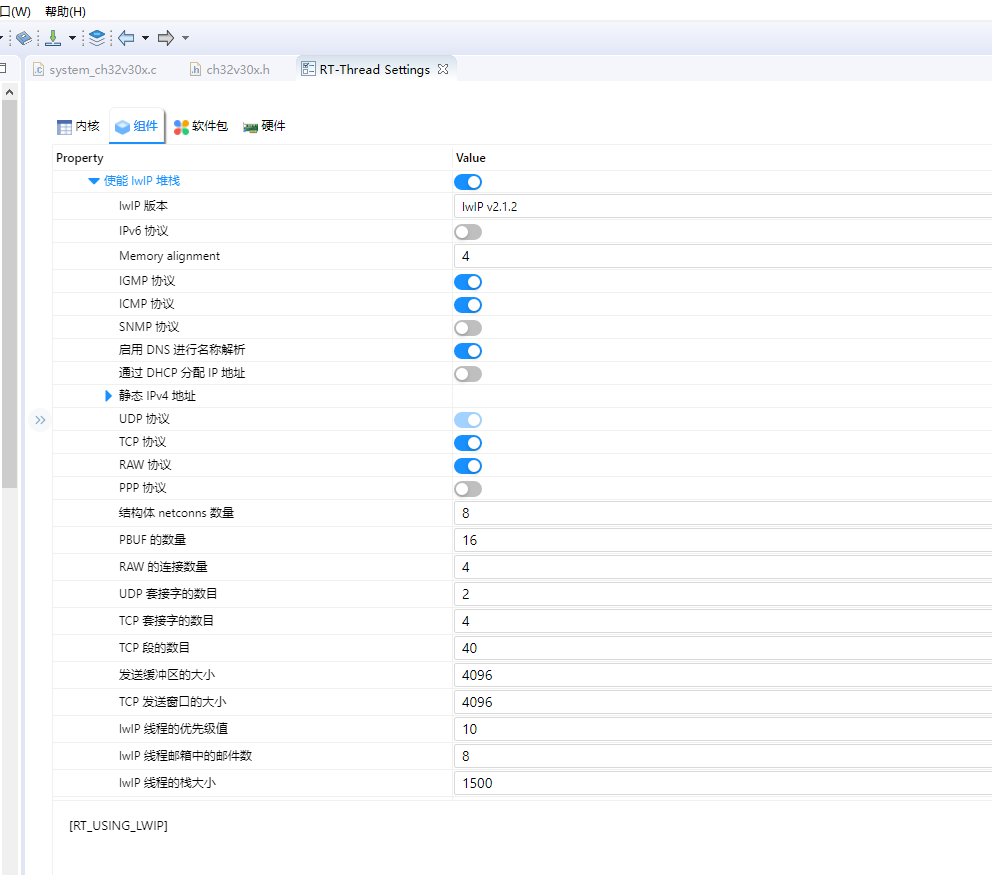

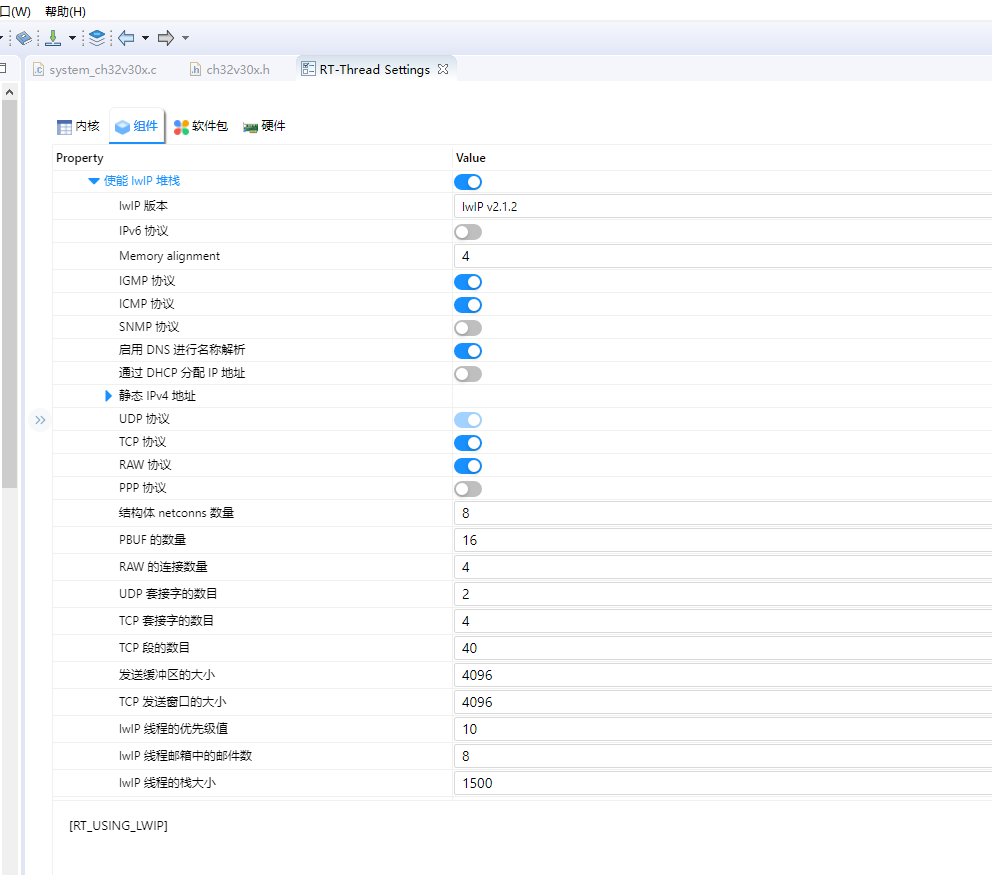

rom和ram分布

rom和ram分布

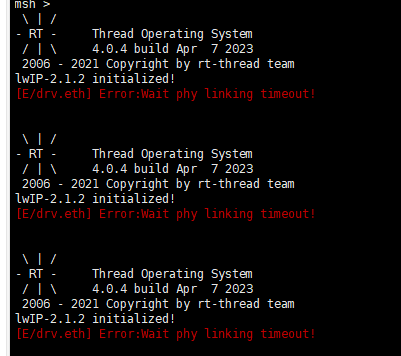

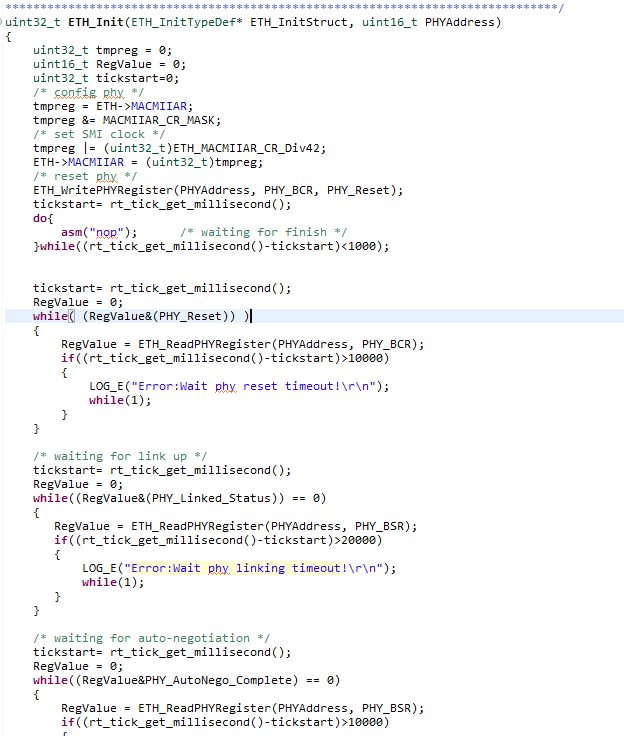

ch32v307 内部10M PHY层建立链接失败 - 沁恒微电子社区 (wch.cn)我的和他的有一点像,我的是怎么都会卡在这里,换了两个芯片网口都是一样的,我认为不是代码的问题,可能是芯片的问题,如果我的原理图没问题的话,我觉得可以把PCB寄过来帮忙测试下,排查下是什么问题

只要不插网线就不会卡住,但是插上网线之后也没什么反应,也不能用

要么3.3V电源不稳定或者纹波过大,毕竟看那3.3V电源的1uF电容感觉很不合理。

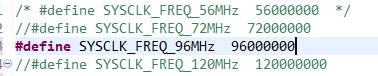

还有,就是为啥不把主频按72M、144M这种很正统的分配频率,而要用96M这种?

你的代码有点乱,风格也不统一

内部PHY 需要60M时钟,官网历程是是按8M晶振配置的,如果12M晶振需要改eth_driver.c文件中 ETH_SetClock()函数 倍频系数,将RCC_PLL3Mul_15改为 RCC_PLL3Mul_10 试下

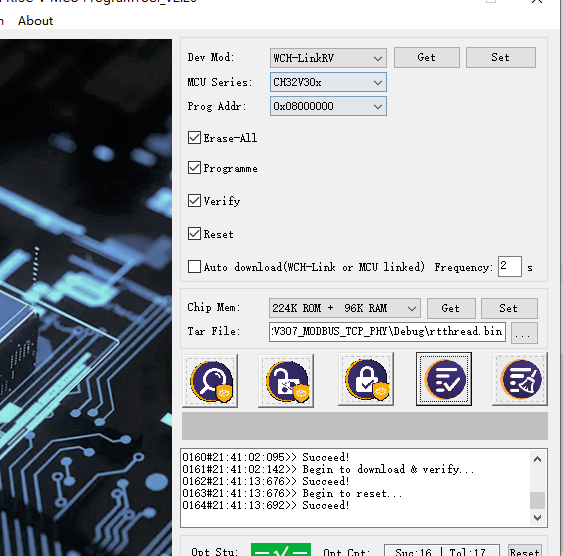

代码是rt-thread ch32v307的bsp源码

开发板原理图上是这个样子的

开发板原理图上是这个样子的

晶振用的12M,使用144就不能用,使用96M才正常,这个我没仔细研究

@7楼 谢谢,我立马试试

7楼说的对!!!感谢七楼