DCDC启用时,VIO33可否不接入外部3.3v,使其悬空或仅接入退耦电容?

使用4.2V的单节锂电池供电时,可否不使用外部稳压电路,可否稳定工作?

设VIO33&VDD33均为4.2V,DCDC启用,此时GPIO高电平为多少V?当DCDC未启用时呢?

热门产品 :

CH397: 高集成度、低功耗USB网卡芯片

DCDC启用时,VIO33可否不接入外部3.3v,使其悬空或仅接入退耦电容?

使用4.2V的单节锂电池供电时,可否不使用外部稳压电路,可否稳定工作?

设VIO33&VDD33均为4.2V,DCDC启用,此时GPIO高电平为多少V?当DCDC未启用时呢?

此外,ADC的校准在不依赖外部基准源的情况下应如何实现?

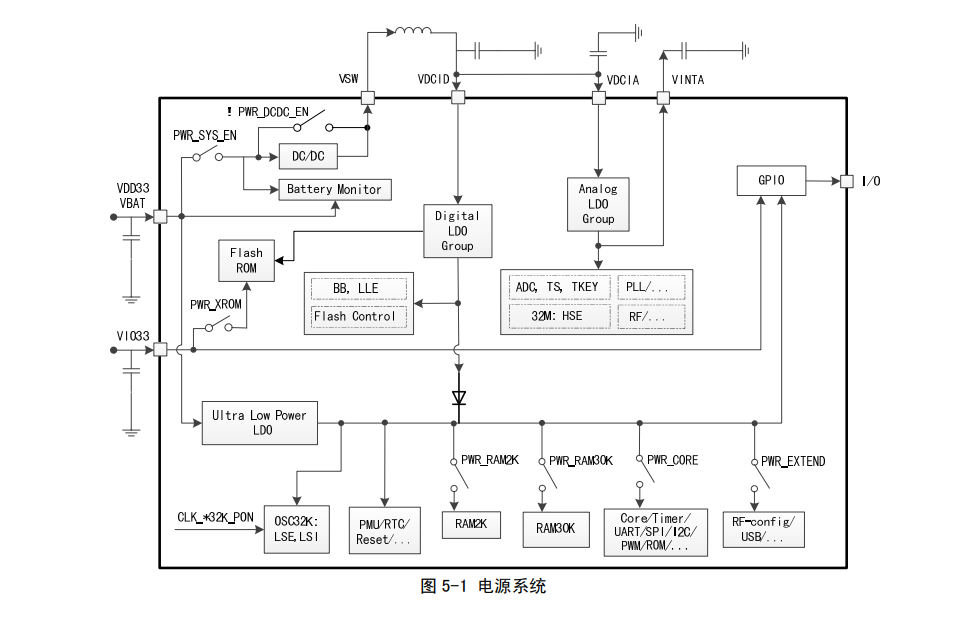

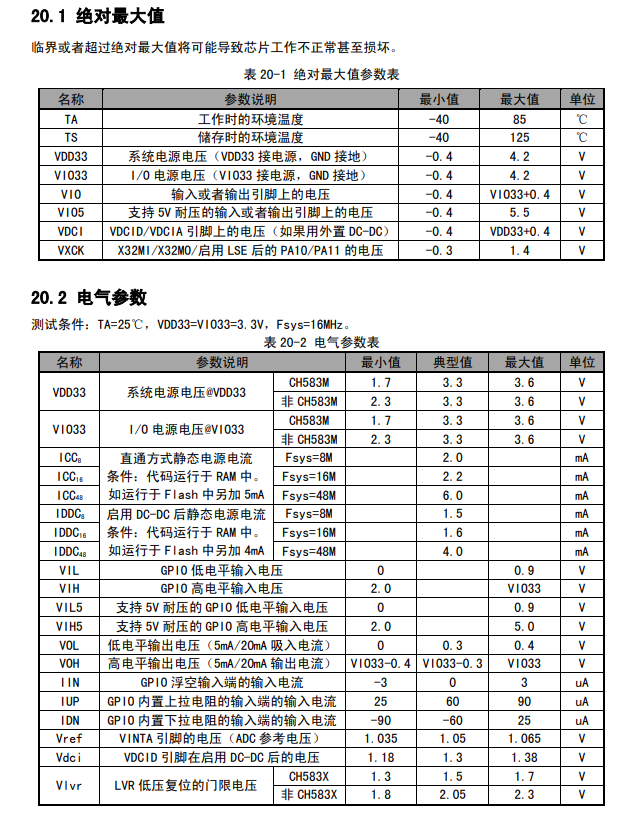

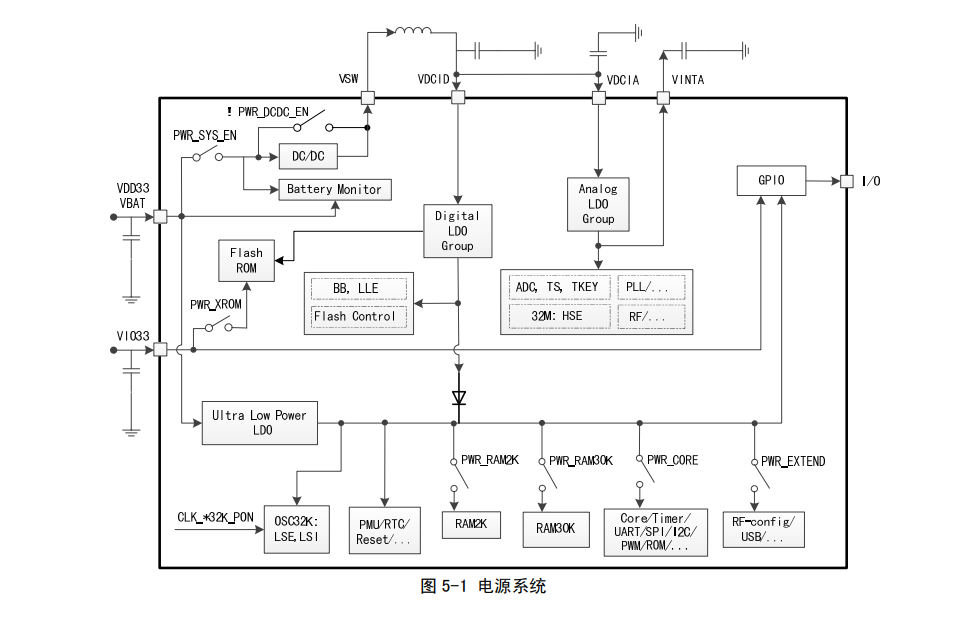

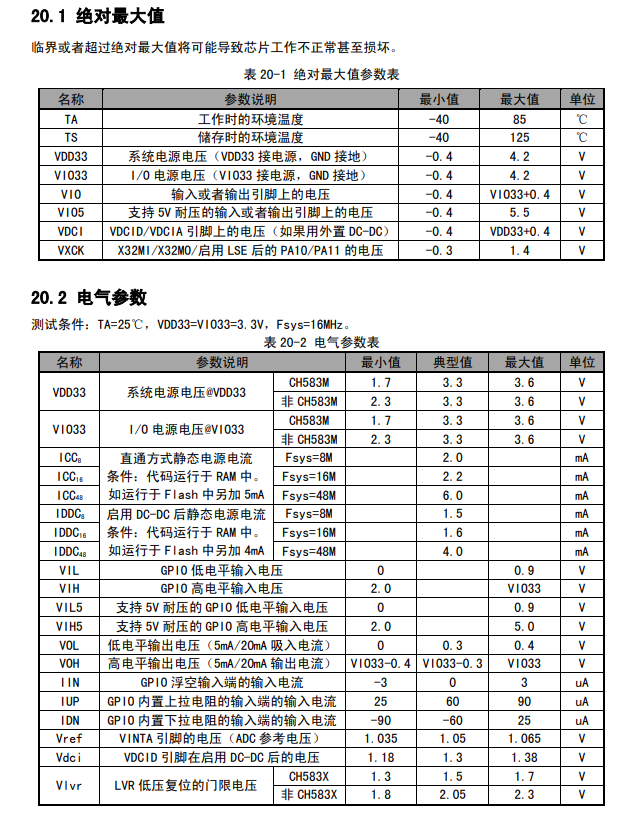

CH582的DCDC功能是节省功耗用的,是否开启DCDC与供电无关系的(开启DCDC需要一颗电感)。芯片需要正常工作则需要供电,提供在CH582标准范围内的供电即可:【2.3-3.6V】。

4.2V供电,需要进行降压,确保给到芯片引脚在标准供电范围内即可。

GPIO引脚的高电平是供电的电压。与DCDC无关的,可以先查看手册理解DCDC的含义。

ADC测试需要根据vinta引脚电压:内部模拟电路的电源节点 VINTA 的实际电压值,通常为 1.05V±0.015V。

可以参考博客,对硬件绘制会有帮助: