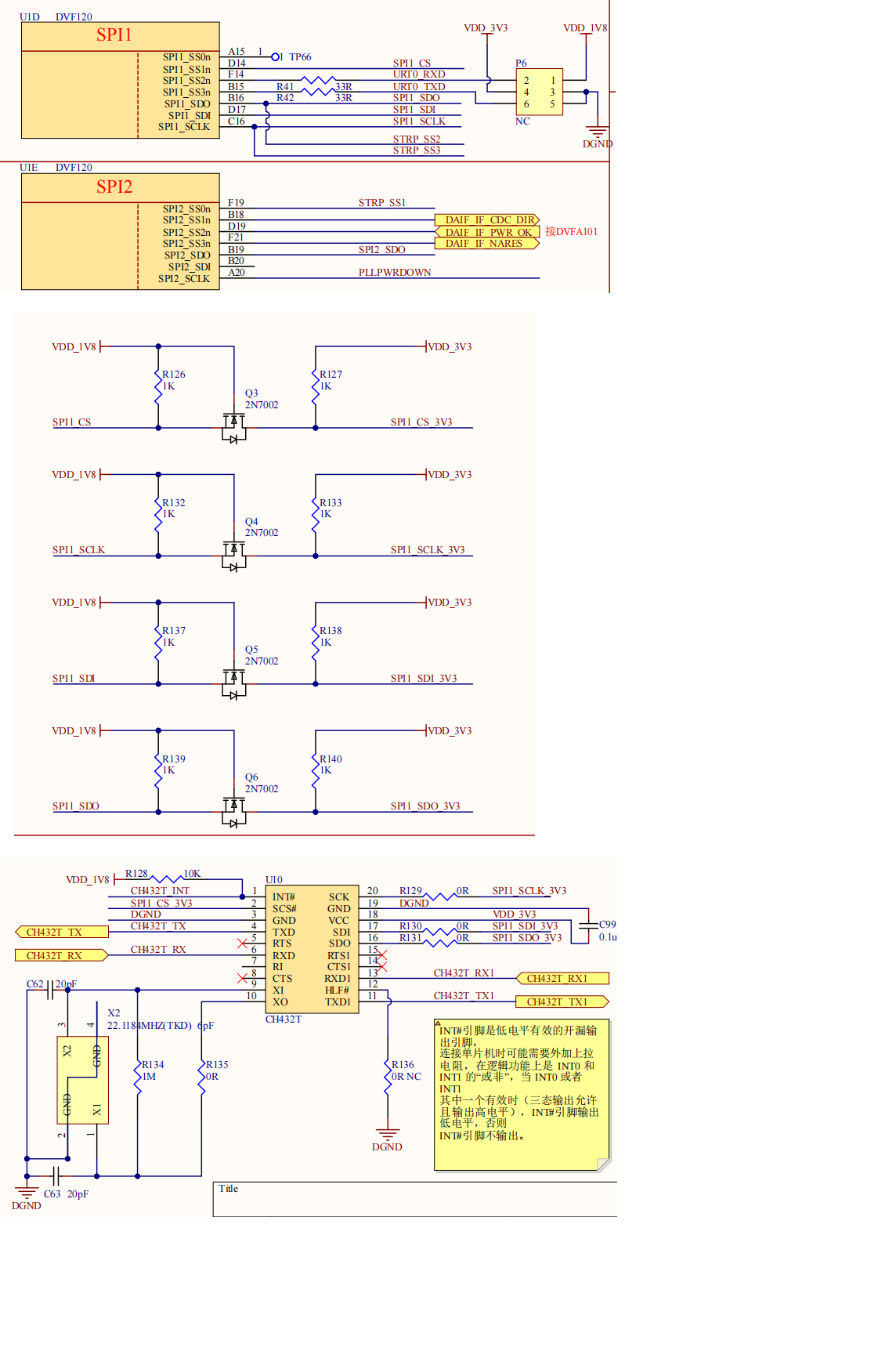

使用官方提供的ch432t linux驱动(ch432ser_linux/ch432.c at main · WCHSoftGroup/ch432ser_linux · GitHub),ch43x_spi_test测试无法通过。无论我们怎么设置spi的频率,都不行。

但是,当我们在ch43x_spi_test接口中增加9秒的读写寄存器操作后,5MHz(含)以下的频率,能够正常通信,应用层上的串口也正常。此时如果把spi频率大于5MHz时,ch43x_spi_test将失败;

tatic int ch43x_spi_test(struct uart_port *port)

{

.....

// 增加start。。。。

u8 cnt=3'

while(cnt--)

{

ch43x_port_write(port, CH43X_SPR_REG, 0x55);

mdelay(1500);

ch43x_port_read(port, CH43X_SPR_REG);

mdelay(1500);

}

// 增加end。。。。

ch43x_port_write(port, CH43X_SPR_REG, 0x55);

val = ch43x_port_read(port, CH43X_SPR_REG);

if (val != 0x55) {

dev_err(&s->spi_dev->dev, "UART %d SPR Test Failed.\n", port->line);

return -1;

}

....

}