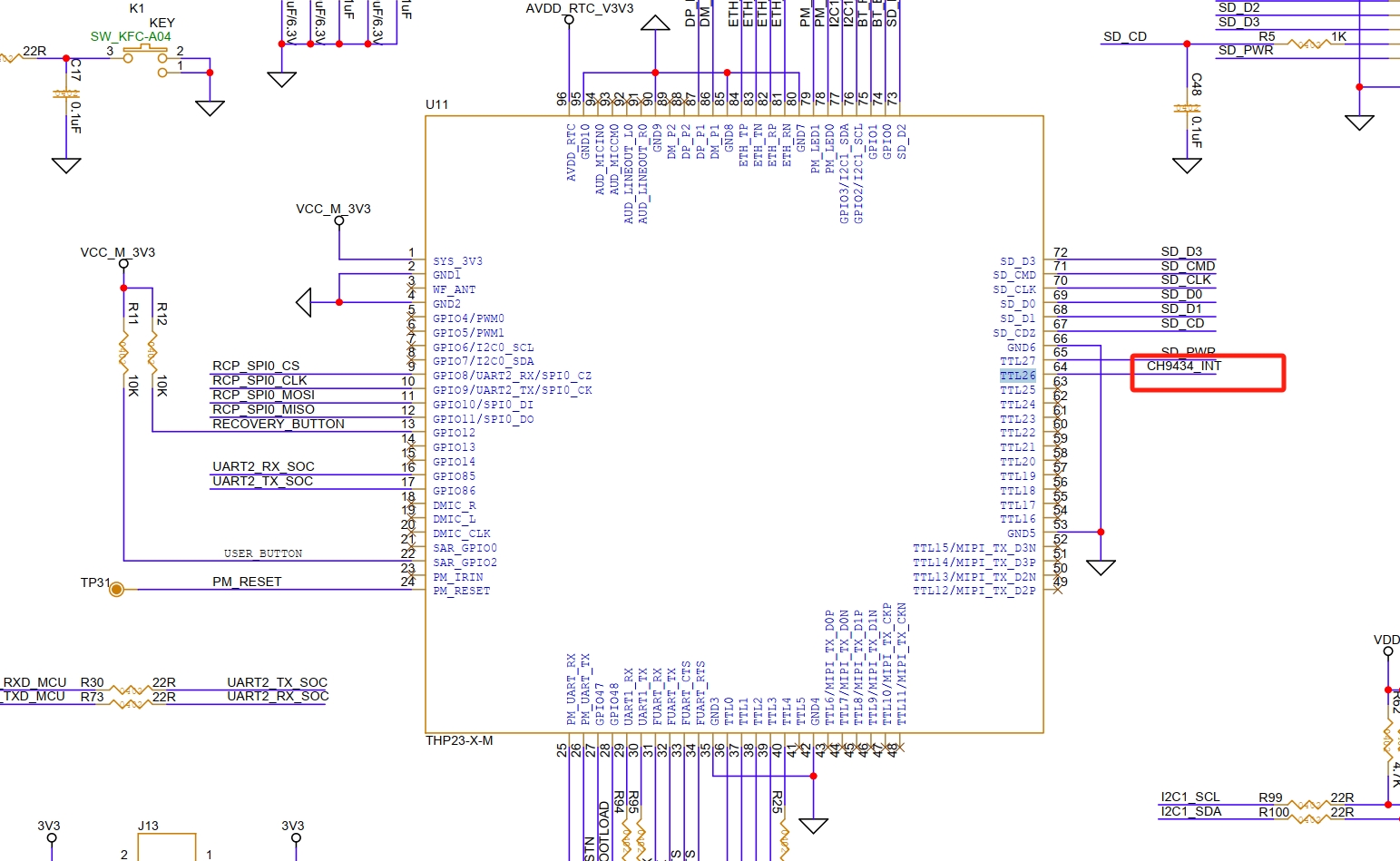

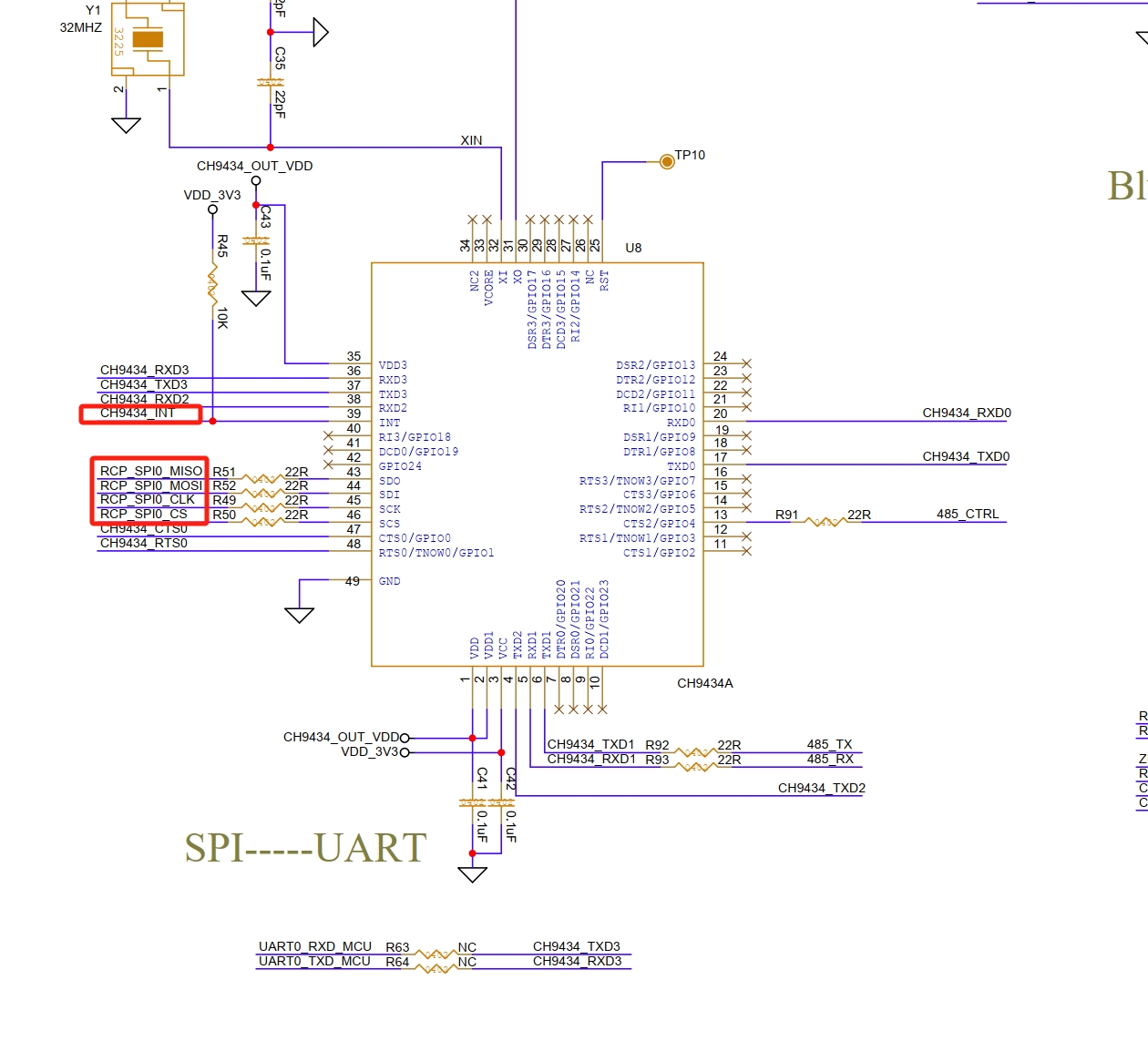

硬件原理图如下:

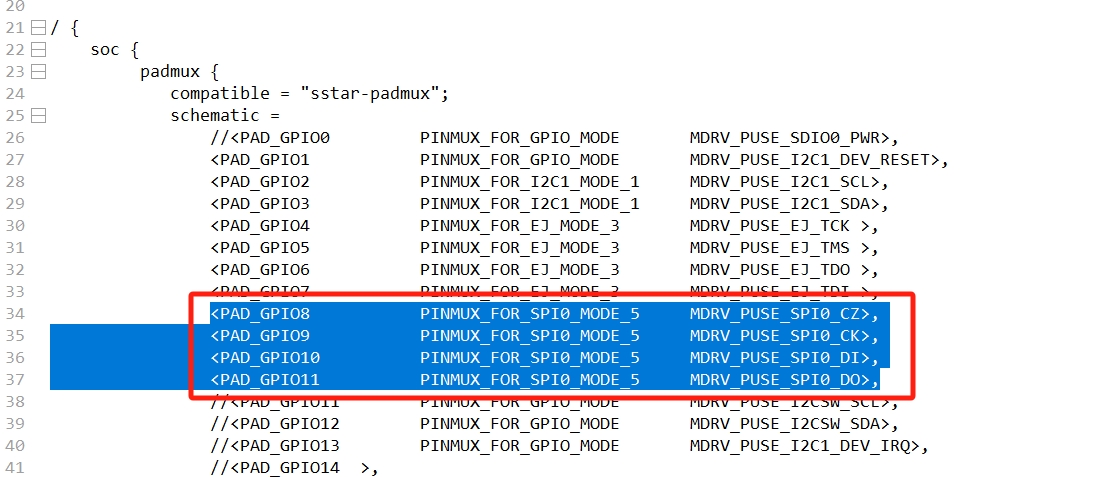

CH9434的INT接SSD202D的TTL26,CS,CLK,MOSI,MISO,分别接SSD202D的GPIO8,GPIO9,GPIO10,GPIO11 。

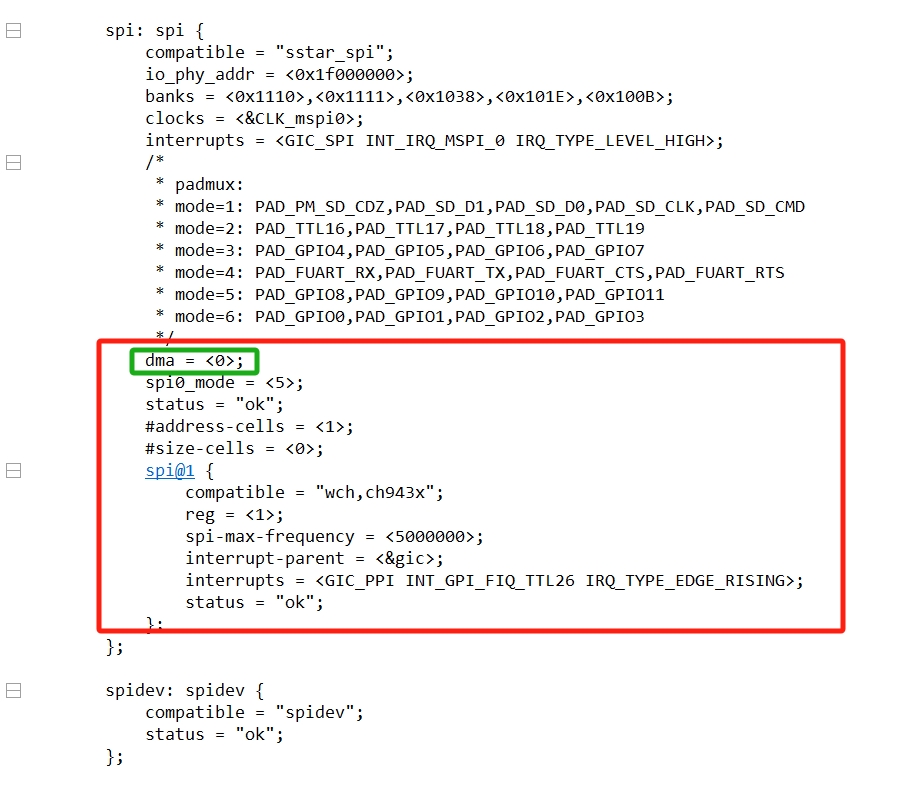

参考SPI使用参考 - SigmaStarDocs (comake.online),修改DTS,

修改arch\arm\boot\dts\infinity2m-ssc011a-s01a-padmux.dtsi

,

,

,

,

把相关管脚复用成SPI,编译kernel烧进板子后,会有/dev/spidev0.0节点。

参考恒沁官网驱动,修改ch9434驱动,

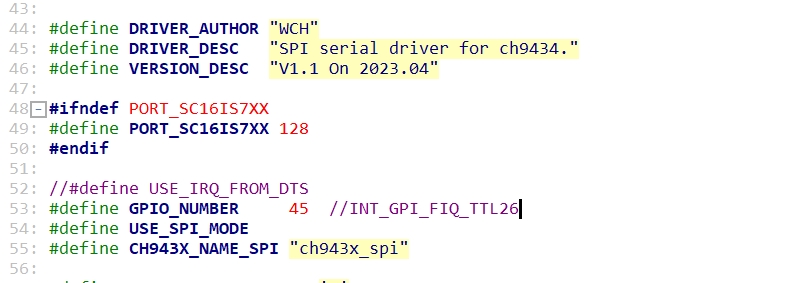

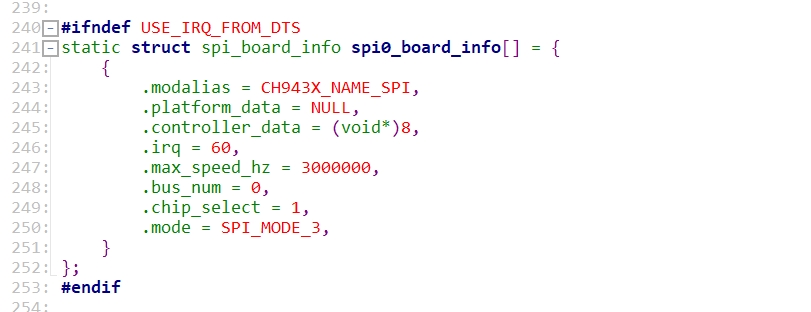

1:屏蔽DTS,增加spi_info

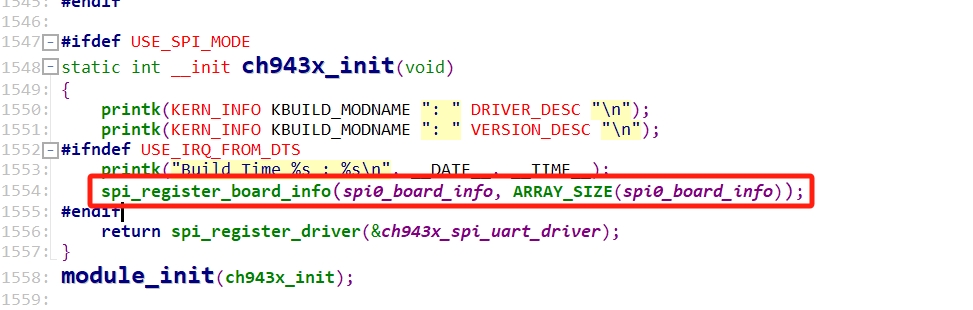

2:增加spi_register_board_info

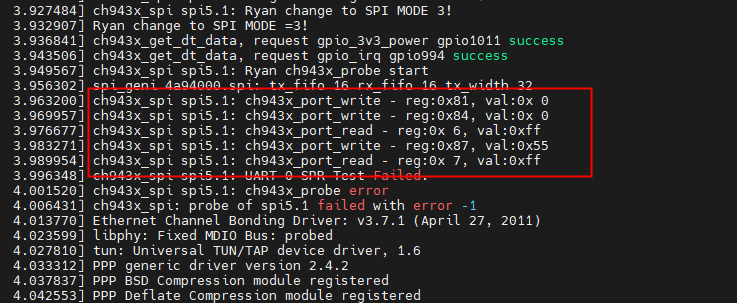

把驱动编译进内核后,跑起来后ch943x_scr_test一直不过。

把驱动编译进内核后,跑起来后ch943x_scr_test一直不过。

[ 1.837296] [ss_gpi_intc_domain_alloc] hw:30 -> v:62

[ 1.839409] gpio_to_irq:62, spi->irq:60

[ 1.843310] change to SPI MODE 3!

[ 1.846561] [Padmux]reset Pad_45(reg 0x101e0d; mask0xf00) to GPIO(org: TTL_MODE_1)

[ 1.854279] ch943x_port_write - reg:0x81, val:0x 0

[ 1.858940] ch943x_port_write - reg:0x84, val:0x 0

[ 1.863760] ch943x_port_read - reg:0x 6, val:0xc7

[ 1.868389] ******Uart 0 SPR Test Start******

[ 1.872791] ch943x_port_write - reg:0x87, val:0x55

[ 1.877567] ch943x_port_read - reg:0x 7, val:0xc7

[ 1.882253] UART 0 SPR Test Failed.

[ 1.885725] ch943x_spi spi0.1: ch943x_probe error

[ 1.890431] ch943x_spi: probe of spi0.1 failed with error -1

spi_board_info中的irq以及其controller_data不知道如何取值。不清楚这样修改是否正确?还请大神给与解答。

2:还需要修改公版DTS中的dma(默认是1,需要屏蔽或者修改成0,原因未知)

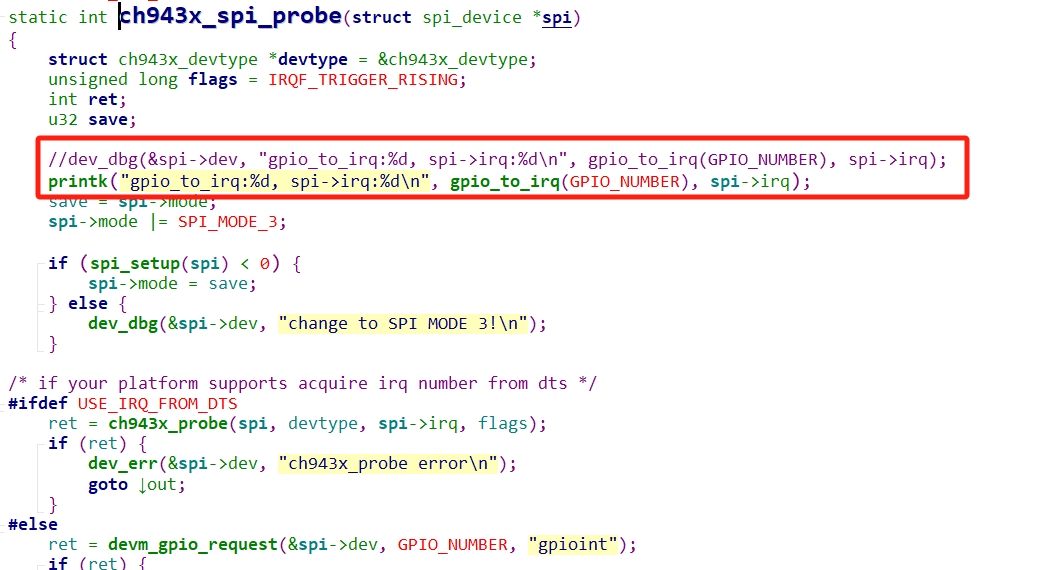

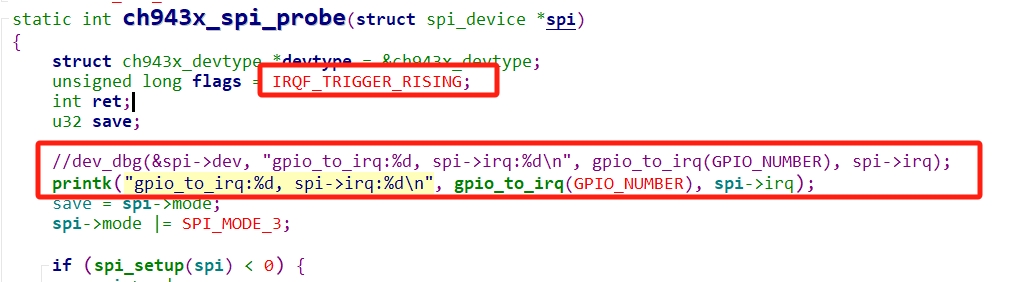

2:还需要修改公版DTS中的dma(默认是1,需要屏蔽或者修改成0,原因未知) 3:修改驱动中ch943x_spi_probe函数,把函数刚开始的dev_dbg换成printk,否则ch943x_scr_test也过不了。

3:修改驱动中ch943x_spi_probe函数,把函数刚开始的dev_dbg换成printk,否则ch943x_scr_test也过不了。

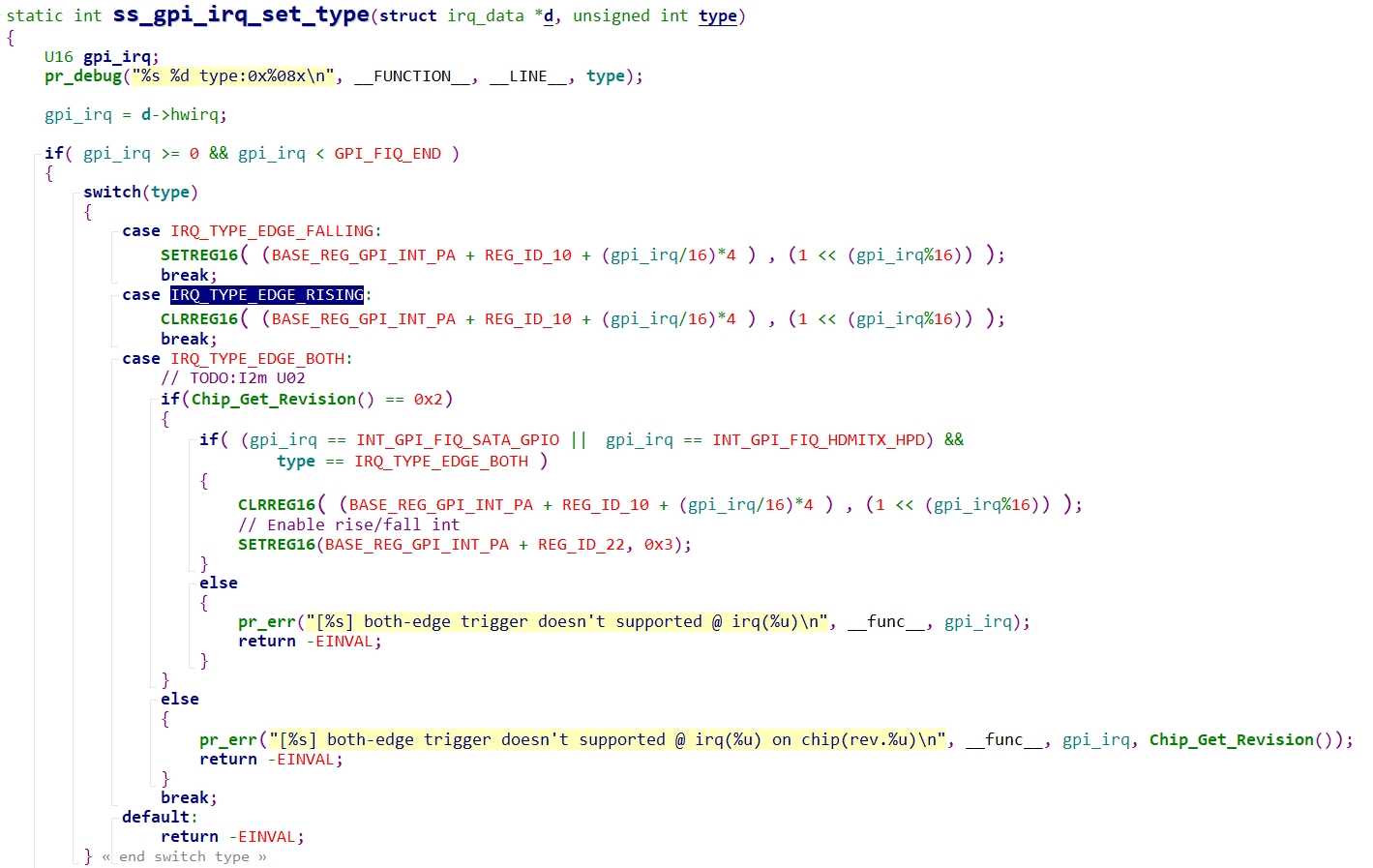

根据irq-gpi.c中代码,只支持IRQ_TYPE_EDGE_FALLING和IRQ_TYPE_EDGE_RISING,实测只有IRQ_TYPE_EDGE_RISING才能正常。

根据irq-gpi.c中代码,只支持IRQ_TYPE_EDGE_FALLING和IRQ_TYPE_EDGE_RISING,实测只有IRQ_TYPE_EDGE_RISING才能正常。