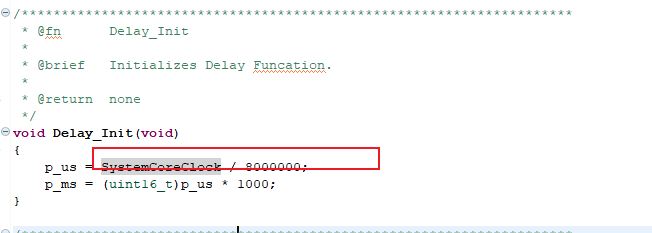

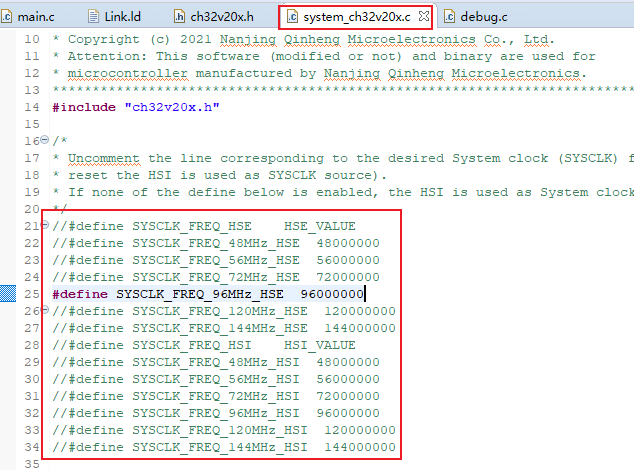

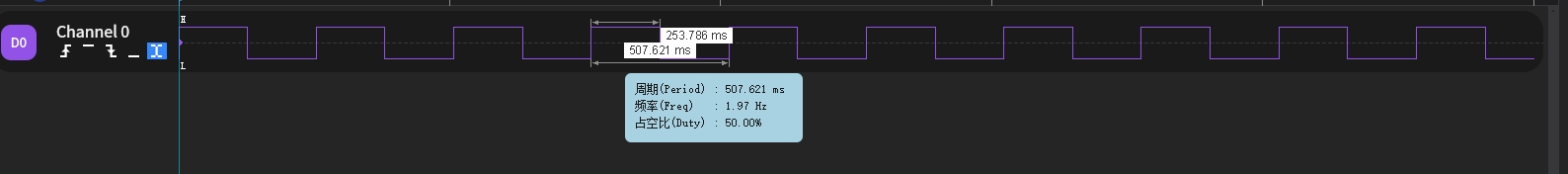

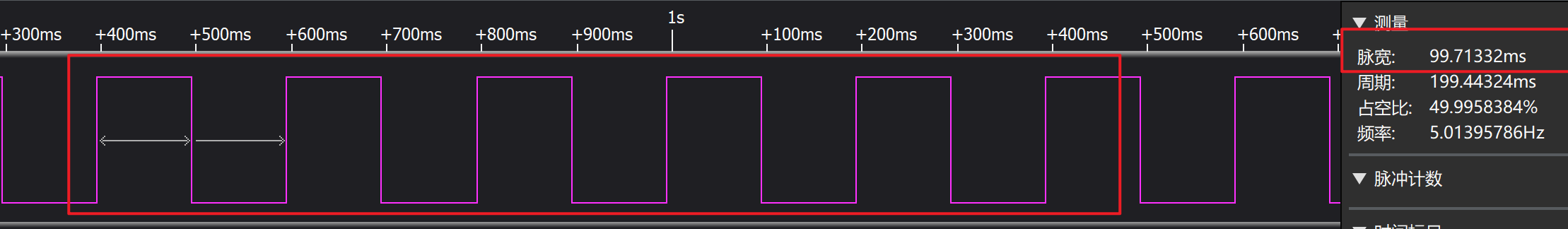

请问如何设置能够消除误差?延时函数使用的是EVT中的示例:

void Delay_Ms(uint32_t n)

{

uint32_t i;

SysTick->SR &= ~(1 << 0);

i = (uint32_t)n * p_ms;

SysTick->CMP = i;

SysTick->CTLR |= (1 << 4);

SysTick->CTLR |= (1 << 5) | (1 << 0);

while((SysTick->SR & (1 << 0)) != (1 << 0));

SysTick->CTLR &= ~(1 << 0);

}