你好,

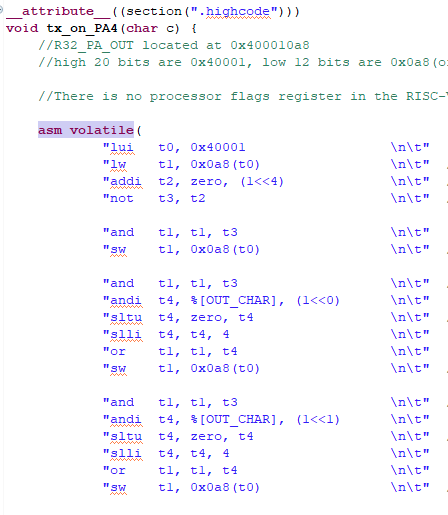

我在测试使用CH573嵌入汇编来生成高速串口信号,方便使用逻辑分析仪调试程序。

类似的代码在8051(CH552),AVR(ATMEGA328P),ARM(samd21,在RAM中运行)都没有问题,每位的输出都是和用指令手册上的速度算出来相一致。

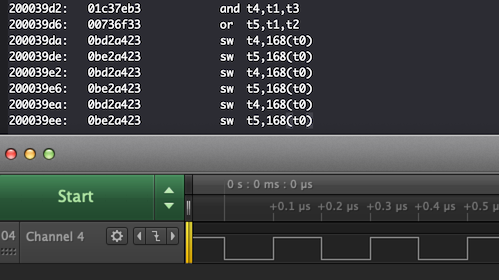

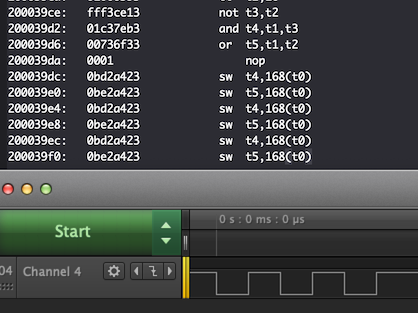

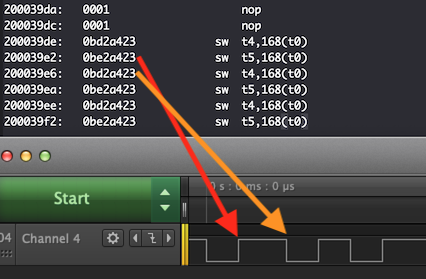

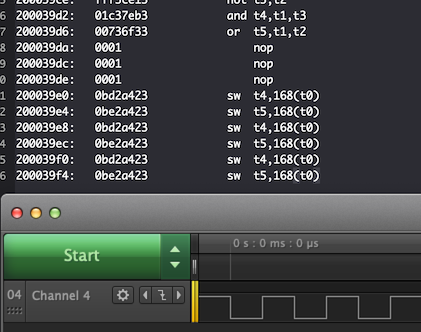

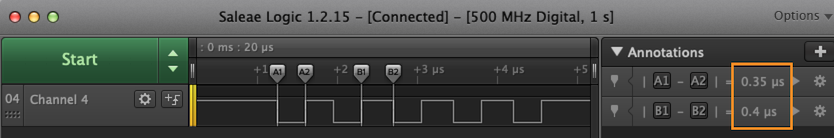

但是在CH573上却做不到这一点。测试的时钟是20M,每个时钟周期为0.05us,每位输出使用6指令。

从逻辑分析仪上可以看出来,有的位输出是7时钟,有的是8时钟,并不统一。我没有找到像“CH55X 汇编指令周期表”这样的文件解释指令周期的问题。请问是不是有缓存命中,对齐,或者是其他的问题?是否有办法加以改善?